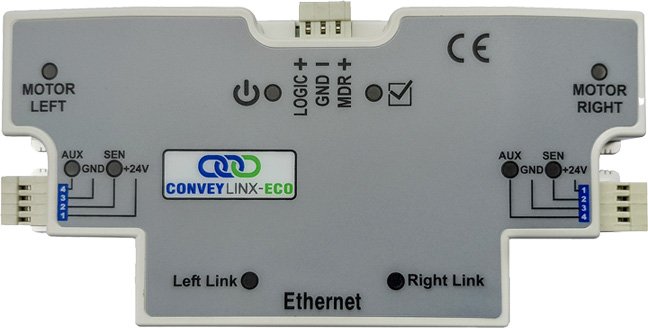

PLC Developers Guide / PLC I/O Mode Control / PLC Inputs for PLC I/O Mode /

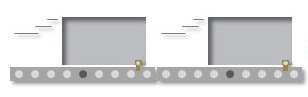

Port Inputs |

ConveyLinx ERSC ✅ | ConveyLinx-Ai 24V ✅ | ConveyLinx-Ai 48V ✅ |

|

|

|

|

| ConveyLinx-ECO ✅ | ZPA Mode ❌ | PLC I/O Mode ✅ | |

|

|

|

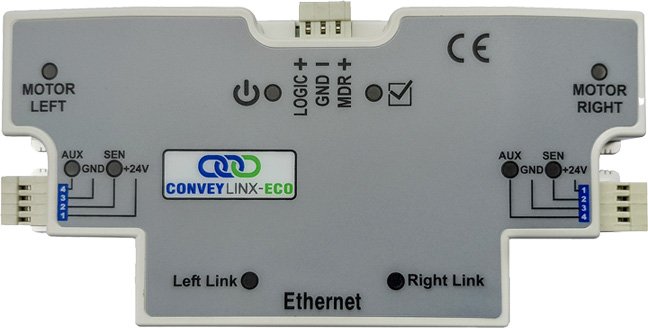

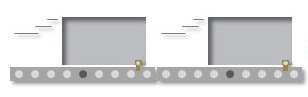

Port Inputs |

ConveyLinx ERSC ✅ | ConveyLinx-Ai 24V ✅ | ConveyLinx-Ai 48V ✅ |

|

|

|

|

| ConveyLinx-ECO ✅ | ZPA Mode ❌ | PLC I/O Mode ✅ | |

|

|

|